Die Hexzahlen Eingabe des ram Befehls funktioniert schon.

Archiv der Kategorie: Einplatinencomputer

Propeller Chip Locks – Grundlagen

Wenn zwei Cog’s auf den gleichen Speicherbereich zugreifen verhindert der Propeller eigenständig Kollisionen wenn es sich nur um einzelne Byte, Wort oder Langwort Zugriffe handelt. Diese Zugriffe eines Cog’s werden erst abgearbeitet bevor der nächste Cog Zugriff bekommt.

Wenn ein Cog jedoch in einer Schleife einen Block von Daten schreibt und ein anderer Cog diesen Datenblock zugleich liest, kann der Propeller nicht mehr sicherstellen, das alle Daten beim lesen zuvor komplett geschrieben wurden, da die HUB Rotation einfach weiter läuft.

- Routinen die exclusiven Zugriff auf einen Hauptspeicherbereich benötigen benutzen den LOCKNEW Befehl der einen Wert zurückgibt (-1=ERROR ansonsten eine Lock-ID). Nur ein Cog sollte den LOCKNEW Befehl ausführen, dieser Cog sollte die Lock-ID auch an alle anderen Cog’s kommunizieren die diesen Speicherbereich benutzen

- Jeder Cog der auf diesen Speicherbereich zugreifen will muss zuvor erfolgreich die Lock-ID sperren. Ein erfolgreiches Sperren wird durch den Rückgabewert FALSE des LOCKSET (Lock-ID) Befehls angezeigt. Falls LOCKSET TRUE zurückgibt beansprucht gerade ein anderer Cog den Speicherbereich. Der Cog muss warten bis ein LOCKSET Befehl erfolgreich ist

- Der Cog der einen LOCKSET Befehl erfolgreich ausführt, kann den Speicherbereich nach belieben benutzen. Wenn dessen Bearbeitung fertig ist muss der Speicherbereich mittels LOCKCLR (Lock-ID) wieder freigegeben werden, damit andere Prozesse wieder auf den Speicherbereich zugreiffen können. In einem sauberen System kann der Rückgabewert von LOCKCLR ignoriert werden, solange der freigebende Cog der einzige mit der Berechtigung war, die Sperre aufzuheben.

- Wenn ein Speicherbereich nicht länger benötigt wird sollte die darauf bezogene Sperre mittels LOCKRET (Lock-ID) wieder zurückgegeben werden. Normalerweise geschieht das durch den Cog der den LOCKNEW Befehl gegeben hat.

Zu beachten ist, daß der Haupspeicherzugriff nicht wirklich geblockt wird. Weder vom HUB oder dem Lock. Es liegt also an den einzelnen Prozessen die Regeln einzuhalten. Auch ordnet der HUB einen LOCKNEW Befehl nicht dem aufrufenden Cog zu. Jeder andere Cog kann Locks wieder freigeben.

Einplatinencomputer mit 6504 CPU

Hier noch ein von mir gebauter Einplatinencomputer mit der 6504 CPU. Die CPU ist kleiner, hat weniger PIN’s als die 6502 CPU und kann auch nur 8kByte Speicher adressieren. Die 6502 CPU kann 64kByte Speicher adressieren.

Bestückt ist das Board mit einem 2kByte 6116 SRAM Chip, einer 8255 PIO und der 6551 SIO mit nachgeschaltetem MAX 232 (leerer 16 pol. Sockel). Oben rechts sieht man ein zugeklebtes EPROM. Das EPROM diente hier als MMU (Memory Management Unit) um den knappen Adressbereich der 6504 besser ausnutzen zu können.

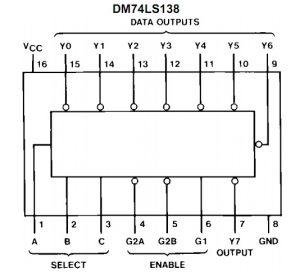

Bei meinen ersten Einplatinencomputern hatte ich immer einen 74LS138 Chip (Demultiplexer) benutzt um die CS (Chip Select) Signale aus den oberen drei Adressbits zu generieren.Das hat jedoch den Nachteil, das man den gesamten Adreßbereich der CPU in 8 gleichgroße Bereiche teilen muss. Der Adreßbereich einer 6502 ist 64kByte, geteilt durch 8 wären das Speicherblöcke von je 8kByte größe. Das ist geradezu verschwenderisch wenn man nur eine PIO oder SIO adressieren will, die gerade einmal zwei oder drei ansprechbare Register besitzen.

Also habe ich ein EPROM genommen, welches sehr viel mehr Adreßleitungen aufnehmen kann, und mit seinem 8-Bit Datenbus quasi eine programmierbare Speicherbereich Zuweisung ermöglicht. Ich erinnere mich die oberen 8 Adressleitungen der CPU zur MMU geführt zu haben, das ermöglichte bei 64kByte eine Blockgröße von nur noch 256 Byte. Mit der Programmierung des EPROM habe ich ihm Einplatinencomputer mit 6504 CPU weiterlesen

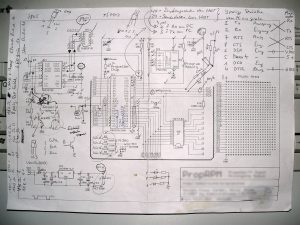

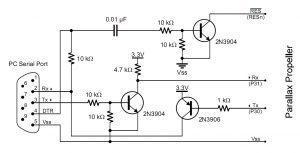

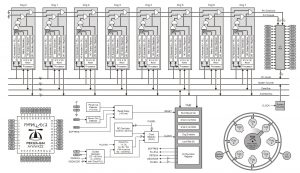

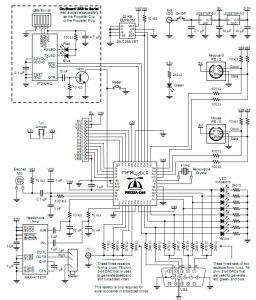

Propeller Chip – Schaltpläne

Propeller Oszillator – Grundlagen

System Takt

Die internen Funktionen des Propeller Chip werden von einem System Takt kontrolliert der bestimmt wie schnell der Propeller läuft und wie schnell die Ausführung von Programmen ist.

Es gibt vier Taktquellen von denen der System Takt abgeleitet werden kann

- der interne langsame Oszillator (RCSLOW 20kHz)

- der interne schnelle Oszillator (RCFAST 12MHz)

- einem Quarz oder Schwingkreis

- einem Frequenzgenerator

Benutzt man einen Quarz, Schwingkreis oder einen Frequenzgenerator kann zusätzlich ein PLL aktiviert werden, der den System Takt 16fach beschleunigt.

Der System Takt kann bis zu 80MHz betragen. Bis 100MHz läuft der Propeller unter normalen Bedingungen noch stabil. Höhere Frequenzen lassen den Propeller instabil werden.

RCSLOW

Wenn der Propeller Chip theoretisch mit 20kHz läuft, kann sich der Takt in Wirklichkeit zwischen 13kHz und 33kHz befinden (Hersteller Toleranzen).

Der Oszillator ist über kurze Zeitspannen recht stabil. Allerdings verschiebt sich die Taktfrequenz mit der Zeit. Das ist hauptsächlich abhängig von der Temperatur des Propeller Chip und dessen Versorgungsspannung.

Für einen präzisen und stabilen Systemtakt ist ein externer Quarz, Schwingkreis oder Frequenzgenerator unabdingbar.

RCFAST

Wenn der interne Oszillator mit 12MHz läuft sind es in der Realität zwischen 8MHz und 20MHz.

Der Propeller Chip benutzt den RCFAST Oszillator beim Bootvorgang und wenn er ein Programm von einem PC empfängt. Um die Takt Werkstoleranzen der Propeller Chips auszugleichen benutzt das Empfangsprotokoll einen Mechanismus der kein 100 Prozent genaues Timing benötigt.

Quarz oder Schwingkreis

Der Propeller unterstützt das direkte anschließen eines Quarz oder Schwingkreises mit Frequenzen von 0 bis 80MHz. Ist der interne PLL aktiviert muss die Frequenz des externen Taktgebers zwischen 4MHz und 10MHz liegen. Bei einem externen Frequenzgenerator werden keine Kondensatoren benötigt. Sein Ausgang wird einfach an den entsprechenden Propeller PIN angeschaltet.

Frequenzgenerator Modul

Der Propeller unterstützt das direkte anschalten eines Frequenzgenerators mit einer Frequenz von 0 bis 128MHz. Ist der interne PLL aktiviert muss der externe Takt zwischen 4MHz und 10MHz liegen.

PLL

Ist der interne PLL aktiviert kann er einen externen Takt bis zu einem Faktor von 16 beschleunigen. Der PLL Schaltkreis multipliziert den externen Takt immer 16fach und ein nachgeschalteter Teiler erzeugt den finalen Systemtakt. Der PLL erzeugt Frequenzen von 64MHz bis 160MHz. Das erfordert einen externen Takt zwischen 4MHz und 10MHz. Der höchste Systemtakt sollte 80MHz betragen. Das erfordert eine Teilung des Taktes hinter dem PLL die einen Takt von maximal 80MHz erzeugt.

Das bedeutet wenn der PLL aktiviert ist sollte der externe Takt nur in einem bestimmten Bereich liegen, maximal 10MHz. Wenn man einen Systemtakt von 80MHz benötigt, braucht man einen externen Takt von 5MHz (5*16/1) oder 10MHz (10*16/2).

In der Praxis kann der Systemtakt problemlos 96MHz (6MHz extern) erreichen. Die Firma Parallax berichtet das alle Propeller Chips einen Test mit 104MHz absolvieren müssen.

| externe Frequenz | PLL Teiler 2 | PLL Teiler 1 |

| 4MHz | 32MHz | 64MHz |

| 5MHz | 40MHz | 80MHz |

| 6MHz | 48MHz | 96MHz |

| 6.25MHz | 50MHz | 100MHz |

| 6.5MHz | 52MHz | 104MHz |

| 7.3728MHz | 59MHz | 118MHz |

| 8MHz | 64MHz | verboten |

| 10MHz | 80MHz | verboten |

| 14.31818MHz | 114.5MHz | verboten |

Propeller Interrupts – Grundlagen

Der Propeller Chip besitzt keine Interrupt Eingänge wie andere Microkontroller. Alle externen Ereignisse müssen wiederholt abgefragt werden oder es muss auf ein High oder Low an einem Port PIN gewartet werden. Für die Mehrkern Architektur des Propeller stellt das aber kein Problem dar. Man stellt einfach einen oder mehrere Cog’s zur Interrupt Verwaltung ab. Diese(r) wartet in einer Schleife bis die gewünschten Interrupt Ereignisse eintreten während in den anderen Cog’s weitere Programme unbeeinflusst ablaufen.

Bei mehreren Interrupts deren Timing unkritisch ist kann ein Cog mit einer zyklischen Abfrage auf mehrere Ereignisse reagieren. Kritische Interrupts können von einem einzelnen Cog binnen weniger Taktzyklen erfasst werden.

Ein Propeller Chip Programm läuft z.B. in einem Cog während andere Cog’s sich um Interrupts kümmern. Da alle Cog’s unabhängig arbeiten können mehrere Interrupts parallel bearbeitet werden. Das kann kein anderer Einkern Microcontroller, ausgenommen solche mit Hardware Interrupt Eingängen.

Da jeder Cog Hardware Zähler besitzt kann man auch kurze Signal Impulse erkennen. Das kann von einem Cog dazu verwendet werden um zyklisch Interrupt Eingänge abzufragen und ein eintreffendes Ereignis quasi nebenher zu bearbeiten.

Ein Cog der zyklisch mehrere Interrupt Eingänge abfragt kann eine eigene Interrupt Priorisierung durchführen. Durch diese zyklische mehrfach Abfrage ist es auch möglich Massnahmen einzuleiten, die auf dem Eintreffen mehrerer gleichzeitiger Interrupts basieren und nicht auf einem einzelnen Interrupt. Die Polarität der Interrupt Eingänge ist nur vom Programm abhängig und kann wenn erforderlich zur Laufzeit geändert werden.

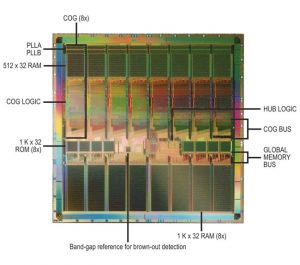

Propeller Cog RAM – Grundlagen

Das Cog RAM ist der Speicher, den jeder Cog für sich alleine hat. Es besteht auf 496 x 32 Bits der für Code und Daten verwendet werden kann. Ferner befinden sich noch 16 spezial Register im RAM. Der USER Speicherbereich geht von $000 bis $1EF und die Spezialregister gehen von $1F0 bis $1FF. Die meisten Befehle beeinflussen alle 32 Bits einer Adresse. Eine Ausnahme stellen Code selbstmodifizierende Befehle wie MOVS, MOVD, MOVI und der CALL sowie JMPRET dar.

- MOVS beeinflusst die unteren 9 Bits (B8 bis B0) einer Cog Speicheradresse ohne die anderen Bits zu verändern

- MOVD macht das selbe mit den nächsten 9 Bits (B17 bis B9) ohne die anderen Bits zu verändern

- MOVI verändert nur die MSB (Most Significant Bits) B31-B23

- CALL und JMPRET beeinflussen ebenfalls die unteren 9 Bits (B8 bis B0) des RET Befehls um die Rückkehr aus einer Assembler Subroutine zu vereinfachen

| B31 – B23 | B22 – B18 | B17 – B9 | B8 – B0 |

| Befehl | Ziel | Quelle | |

| MOVI | MOVD | MOVS, CALL, or JMPRET |

Spezial Register

Addr. |

Name |

Typ |

Funktion |

| $1F0 | PAR | Read-Only | Boot parameter |

| $1F1 | CNT | Read-Only | System Counter |

| $1F2 | INA | Read-Only | Input states for P31-P0 |

| $1F3 | INB | Read-Only | Input states for P63-P32* |

| $1F4 | OUTA | Read/Write | Output States for P31-P0 |

| $1F5 | OUTB | Read/Write | Output states for P63-P32* |

| $1F6 | DIRA | Read/Write | Direction States for P31-P0 |

| $1F7 | DIRB | Read/Write | Direction States for P63-P32* |

| $1F8 | CTRA | Read/Write | Counter A Control |

| $1F9 | CTRB | Read/Write | Counter B Control |

| $1FA | FRQA | Read/Write | Counter A Frequency |

| $1FB | FRQB | Read/Write | Counter B Frequency |

| $1FC | PHSA | Read/Write | Counter A Phase |

| $1FD | PHSB | Read/Write | Counter B Phase |

| $1FE | VCFG | Read/Write | Video Configuration |

| $1FF | VSCL | Read/Write | Video Scale |

* nicht vorhanden im P8X32 Propeller Chip

Propeller Hauptspeicher – Grundlagen

Der 32kByte große Hauptspeicher ist von den RAM’s der einzelnen Cogs separiert.

Ein Programm welches auf einem Cog läuft (egal ob Benutzerprogramm oder der SPIN Interpreter) hat durch die Befehle RDLONG, RDWORD, RDBYTE, WRLONG, WRWORD und WRBYTE Zugriff auf den Hauptspeicher. Diese Befehle werden immer komplett durchgeführt und nie teilweise. Wenn also zwei Cogs nacheinander in den gleichen Hauptspeicherbereich schreiben, so steht dort immer der Wert den der in der zuletzt hineingeschrieben wurde. Dieser Wert ist kein Mischwert aus beiden Schreibzugriffen.

Die Benutzung von Locks hilft einem Cog einen längeren ununterbrochenen Zugriff auf den Hauptspeicher zu bekommen um größere Bereiche des Hauptspeichers zu lesen/beschreiben.

Der Hauptspeicher kann entweder mit 32k x 8 Bits, 16k x 16 Bits, 8k x 32 Bits oder wenn erforderlich eine Mischung aus diesen angesprochen werden. Wenn die Befehle RDLONG oder WRLONG benutzt werden müssen die zwei LSB’s auf null gesetzt werden. Bei den Befehlen RDWORD und WRWORD muss das LSB auf null gesetzt werden.

Der Hauptspeicherinhalt wird beim starten des Propeller von einem externen 32k x 8 Bit I2C EEPROM oder von der Propeller Tool Software einkopiert. Danach startet der SPIN Interpreter im Cog 0, welcher dann beginnt den geladenen SPIN Code auszuführen.

Das externe EEPROM bzw. der vom Tool eingespielte Code muss immer ein SPIN Programm enthalten. Auch wenn dieses SPIN Programm nur dazu dient den Operations Modus des Propeller festzulegen und dann mit anderweitigem Code weiter zu arbeiten.

Der Hauptspeicher enthält keinen ausführbaren Maschinencode wie bei einem normalen Microcontroller. Er enthält nur Daten. Die Interpretation dieser Daten hängt vom laufenden echten Programm in einem der Cog’s ab. Da im Cog 0 zuallererst der SPIN Interpreter startet ist er der Entscheider wie die nachfolgenden Daten interpretiert werden.

Alter 19-Zoll Einplatinencomputer

Auf dem Speicher fand ich noch einen von mir gebautes modulares 19-Zoll Computersystem. Das Netzteil hat eine nachgeschaltete doppelte elektronische Sicherung. Deren Ansprechstrom ist mit einem Potentiometer justierbar. Ist eine solche Sicherung einmal ‘durchgebrannt’ kann man sie nur durch Wegnahme der 220V Versorgung resetten. Der Einplatinencomputer selber ist bestückt mit einer 6502 CPU (4MHz), einer seriellen Schnittstelle SIO 6551und MAX 232 Pegelwandler, einer PIO 8255 und zwei gestapelten SRAM Chips mit getrennt herausgeführten Chipselect Signalen. Ferner ist noch ein ZN429 8-Bit D/A Wandler auf dem Board.

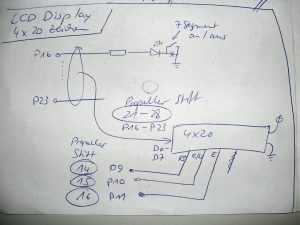

LCD Display funktioniert

15.4.2007

09:00

Ich muss jetzt erstmal die Keycode Zuordnung herausbekommen. Das LCD will ja andere Codes als das Keyboard hergibt (oder ??). Also das LCD-Display will schon ASCII Codes aber der Keyboard Treiber liefert evtl. falsche Werte zurück.

Ich muss jetzt erstmal die Keycode Zuordnung herausbekommen. Das LCD will ja andere Codes als das Keyboard hergibt (oder ??). Also das LCD-Display will schon ASCII Codes aber der Keyboard Treiber liefert evtl. falsche Werte zurück.

14:00

Uhh !! Jetzt habe ich es endlich geschafft einen LCD Display funktioniert weiterlesen